Tín Hiệu Trong Miền Thời Gian và Tần Số — Hai Cách Nhìn Mà AMS Engineer Cần Hiểu Cả Hai

Rise time, bandwidth, và Fourier transform không phải chỉ là lý thuyết tín hiệu. Bài này giải thích tại sao AMS engineer cần chuyển đổi linh hoạt giữa time domain và frequency domain — và những con số cụ thể để build intuition.

Có một câu hỏi mình hay dùng để test intuition của junior engineer: “Nếu rise time của một tín hiệu là 1ns thì bandwidth của nó là bao nhiêu?” Câu trả lời phổ biến nhất là im lặng — hoặc “phải biết thêm thông tin.”

Thực ra có một công thức rất đơn giản để ước lượng. Nhưng để hiểu tại sao công thức đó đúng — và quan trọng hơn, tại sao nó quan trọng với công việc thiết kế — mình cần phải hiểu mối liên hệ giữa time domain và frequency domain.

Đây là thứ Bogatin giải thích rất tốt trong chương 2 của Signal and Power Integrity — Simplified: tín hiệu không phải chỉ có một cách nhìn. Nhìn nó trong miền thời gian là một góc độ. Nhìn nó trong miền tần số là một góc độ khác. Và engineer giỏi cần chuyển đổi tự nhiên giữa hai cách nhìn đó.

Tại sao cần hai domain?

Hãy bắt đầu bằng câu hỏi thực tế: oscilloscope và spectrum analyzer đều đo tín hiệu điện. Nhưng chúng cho ra hai loại thông tin khác nhau hoàn toàn.

Oscilloscope — time domain — cho mình thấy điện áp thay đổi theo thời gian. Mình đọc được: tín hiệu bắt đầu khi nào, lên đến mức cao trong bao lâu, có overshoot không, có ringing không, settling time là bao nhiêu.

Spectrum analyzer — frequency domain — cho mình thấy tín hiệu đó có chứa những tần số nào, mỗi tần số mạnh bao nhiêu. Mình đọc được: năng lượng tập trung ở đâu, có harmonic không, noise floor ở mức nào.

Cùng một tín hiệu, nhưng hai bức tranh hoàn toàn khác nhau. Và mỗi bức tranh trả lời những câu hỏi khác nhau trong thiết kế.

Trong AMS design, mình cần cả hai. Khi debug timing violation thì nhìn oscilloscope. Khi debug EMI hay substrate noise thì cần spectrum. Khi thiết kế bandwidth của một amplifier thì tính trong frequency domain. Khi verify slew rate thì đo trong time domain. Vấn đề là hai domain này không độc lập — chúng là hai mặt của cùng một đồng xu, và mình cần biết cách chuyển từ mặt này sang mặt kia.

Fourier — cây cầu giữa hai domain

Fourier Transform là công cụ toán học chuyển đổi giữa hai domain:

Nhưng thay vì nhìn vào công thức, mình muốn build intuition theo cách Bogatin dùng: mọi tín hiệu đều có thể được xây dựng từ các sóng sine cộng lại với nhau.

Đây là insight quan trọng nhất. Một xung vuông — thứ mà mình thấy hàng ngày trong digital signal — không phải là một thực thể đơn giản trong frequency domain. Nó là tổng của vô số sóng sine với tần số khác nhau:

Tức là một xung vuông không chỉ chứa năng lượng ở — nó chứa năng lượng ở , , , … tất cả các harmonics lẻ, giảm dần theo .

Và đây là nơi mọi thứ bắt đầu liên quan trực tiếp đến thiết kế.

Rise time và bandwidth — công thức engineer cần nhớ

Từ xung vuông lý tưởng đến xung thực tế

Xung vuông lý tưởng có rise time = 0 — tức nó thay đổi từ thấp lên cao ngay lập tức. Trong frequency domain, điều này có nghĩa là nó chứa vô số harmonic với biên độ không bao giờ về 0. Bandwidth của nó là vô hạn.

Xung thực tế thì khác. Rise time luôn có giá trị hữu hạn — do bandwidth hữu hạn của driver, do parasitic capacitance của interconnect, hay do bandwidth của measurement system. Và rise time hữu hạn tương đương với bandwidth hữu hạn trong frequency domain.

Bogatin đưa ra một quy tắc rất thực tế:

Trong đó là rise time đo từ 10% đến 90% của biên độ tín hiệu, và là bandwidth tính bằng Hz khi tính bằng giây.

Tính nhanh với con số cụ thể

Với tín hiệu có rise time :

Với tín hiệu (điển hình trong high-speed SerDes):

Với tín hiệu :

Đây là con số bandwidth tối thiểu mà measurement system của mình phải có để đo chính xác tín hiệu đó. Nếu oscilloscope chỉ có bandwidth mà mình dùng nó đo tín hiệu , thì mình đang đo một tín hiệu đã bị “lọc” mất phần lớn năng lượng cao tần — rise time đo được sẽ chậm hơn thực tế rất nhiều.

Tại sao 0.35?

Con số 0.35 không phải magic — nó đến từ đặc tính của Gaussian filter (hay single-pole RC filter). Với RC filter một pole:

Và rise time của RC filter:

Kết hợp lại:

Vậy là hệ quả trực tiếp của single-pole bandwidth-limiting system. Với Gaussian filter thì hệ số này là . Trong thực tế, là con số an toàn cho hầu hết tín hiệu digital.

Spectrum của tín hiệu trapezoidal — harmonic nào còn quan trọng?

Xung vuông lý tưởng không tồn tại trong thực tế. Tín hiệu thực tế có rise time và fall time hữu hạn — mình gọi là trapezoidal waveform. Về mặt toán học, trapezoidal waveform vẫn chứa vô số harmonic — bandwidth của nó vẫn là vô hạn. Nhưng không phải tất cả harmonic đều quan trọng như nhau.

Bogatin tiếp cận theo câu hỏi thực tế hơn: harmonic nào còn “significant”?

Định nghĩa của ông: một harmonic được coi là significant nếu biên độ của nó trong trapezoidal waveform còn lớn hơn 70% so với biên độ harmonic tương ứng trong ideal square wave. Khi biên độ đã giảm xuống dưới 70% — tức đã bị attenuate hơn — harmonic đó không còn đóng góp đáng kể vào hình dạng của tín hiệu nữa.

Rise time quyết định harmonic nào là harmonic “cuối cùng còn significant.” Harmonic của một xung vuông có tần số . Với trapezoidal waveform có rise time , Bogatin chỉ ra rằng harmonic cao nhất còn significant xấp xỉ tương ứng với bandwidth:

Đây chính là công thức mình đã dùng ở phần trước — nhưng bây giờ mình hiểu rõ hơn ý nghĩa của nó: không phải “tần số cao nhất trong tín hiệu” mà là “tần số cao nhất mà tại đó harmonic còn đủ mạnh để ảnh hưởng đến hình dạng của tín hiệu.”

Rise time kiểm soát harmonic nào còn significant

Lấy ví dụ clock 200 MHz (period ). Ideal square wave của nó có harmonics ở 200 MHz, 600 MHz, 1 GHz, 1.4 GHz… giảm dần theo .

Với driver có :

Tức là chỉ harmonic ở 200 MHz và 600 MHz là còn significant — harmonic thứ ba (1 GHz) đã bị attenuate đáng kể so với ideal square wave. Năng lượng của tín hiệu này tập trung chủ yếu dưới 700 MHz.

Với driver nhanh hơn có :

Giờ thì harmonic ở 200 MHz, 600 MHz, 1 GHz, 1.4 GHz, 1.8 GHz, 2.2 GHz, 2.6 GHz, 3 GHz đều còn significant — nhiều hơn rất nhiều so với driver chậm.

Ứng dụng trực tiếp: EMI và rise time

Đây là insight quan trọng nhất: rise time ngắn hơn làm cho nhiều harmonic cao hơn trở thành significant — tức năng lượng của tín hiệu trải rộng ra đến tần số cao hơn nhiều.

Với driver : harmonics significant đến ~700 MHz

Với driver : harmonics significant đến ~3.5 GHz

Khi team digital tăng tốc driver từ xuống , những harmonic ở 1 GHz, 1.4 GHz, 1.8 GHz… vốn trước đây đã bị attenuate mạnh — giờ trở nên significant. Đây là năng lượng mới xuất hiện ở tần số cao, coupling vào substrate, radiating ra ngoài, và gây EMI.

Đây là lý do EMI engineer luôn lo lắng khi team digital muốn “tăng tốc driver để giảm timing margin” — không phải vì năng lượng tổng tăng lên, mà vì phân bố của năng lượng đó thay đổi: nhiều harmonic cao hơn trở nên đủ mạnh để gây vấn đề.

Hai domain — hai công cụ debug khác nhau

Bây giờ mình có thể trả lời câu hỏi thực tế hơn: khi nào dùng time domain, khi nào dùng frequency domain?

Khi nào nhìn time domain

Debug timing và waveform quality. Overshoot, ringing, settling time, setup và hold time violation — tất cả những thứ này chỉ nhìn thấy được trong time domain. Nếu mình thấy ringing sau rising edge, mình biết có reflection từ impedance discontinuity. Nếu mình thấy settling time dài, mình biết Q factor của hệ thống cao.

Verify slew rate và rise time của driver. Đây là đặc tính time domain trực tiếp. Từ rise time đo được, mình tính để biết tín hiệu này sẽ gây vấn đề gì ở tần số cao.

Debug glitch và transient. Glitch trong tín hiệu analog — ví dụ code dependent glitch trong DAC — chỉ thấy rõ trong time domain với trigger phù hợp.

Khi nào nhìn frequency domain

Debug noise và EMI. Khi mạch analog có noise mà không biết từ đâu, spectrum analyzer sẽ chỉ ra ngay tần số của noise đó. Nếu thấy spike ở , mình biết đó là switching frequency của power supply. Nếu thấy spike ở , mình biết có coupling từ WiFi.

Verify bandwidth của amplifier. AC simulation trong SPICE là frequency domain analysis. Gain và phase margin — những thứ quyết định stability — chỉ rõ ràng khi nhìn trong frequency domain.

Phân tích PDN (Power Delivery Network). Impedance của PDN được đo và spec trong frequency domain. Nếu vượt quá target impedance ở một tần số nào đó, mình biết mạch sẽ có noise ở tần số đó khi có load transient.

Ví dụ thiết kế — chọn bandwidth cho measurement system

Mình đang đo tín hiệu clock với rise time . Oscilloscope mình có bandwidth bao nhiêu là đủ?

Bước 1 — Tính bandwidth của tín hiệu:

Bước 2 — Hiểu tại sao oscilloscope làm chậm rise time

Oscilloscope không phải công cụ đo hoàn hảo — nó có bandwidth hữu hạn của chính nó, tức là nó hoạt động như một low-pass filter đặt giữa tín hiệu thực và màn hình hiển thị. Khi tín hiệu đi qua filter này, các harmonic cao bị attenuate — và hệ quả là rise time trông chậm hơn thực tế.

Nếu oscilloscope có bandwidth , rise time tương đương của nó là:

Ví dụ scope 1 GHz có .

Bước 3 — Công thức cộng bình phương (RSS)

Khi tín hiệu đi qua oscilloscope, rise time tổng mà mình đo được trên màn hình không phải là tổng đơn giản . Với các bandwidth-limiting system có đặc tính Gaussian — và đây là approximation tốt cho hầu hết oscilloscope — rise time tổng được tính theo công thức Root Sum of Squares (RSS):

Intuition của công thức này: mỗi single-pole system làm rộng rise time độc lập với nhau, và khi ghép nhiều hệ thống Gaussian lại thì variance (bình phương) cộng lại — giống như cộng hai phân bố Gaussian độc lập. Kết quả là rise time tổng luôn lớn hơn từng thành phần riêng lẻ, nhưng không lớn bằng tổng tuyến tính.

Bước 4 — Tính sai số và tìm bandwidth cần thiết

Sai số đo rise time là:

Nếu mình muốn sai số dưới 3%, cần tìm thỏa mãn:

Bình phương hai vế:

Tức , hay

Làm tròn an toàn:

Với :

Tương đương bandwidth oscilloscope:

Verify — nếu dùng scope 1 GHz:

, rise time đo được:

Sai số:

Rise time đo được sai hơn 2 lần so với thực tế — và người đo không biết vì số liệu vẫn trông “hợp lý.”

Rule of thumb: Bandwidth oscilloscope nên ít nhất gấp 5 lần bandwidth của tín hiệu cần đo (). Con số này tương đương với — cho sai số dưới 2%, tốt hơn ngưỡng 3% ở trên. Bogatin recommend con số này và mình thấy đúng trong thực tế.

Kết nối với AMS design — tại sao cả hai domain đều cần thiết

Ví dụ 1 — Substrate noise: từ time domain sang frequency domain để tìm

thủ phạm

Đây là tình huống khá phổ biến trong mixed-signal design: mạch analog hoạt động tốt khi test riêng lẻ, nhưng khi tích hợp cùng digital block trên cùng một chip thì output bắt đầu có noise.

Bước 1 — Nhìn oscilloscope trước

Mình connect oscilloscope vào output của amplifier và thấy một ripple định kỳ chồng lên tín hiệu analog — biên độ khoảng 2–3 mV, trông khá đều đặn. Nhìn trong time domain chỉ biết được có noise, không biết từ đâu.

Bước 2 — Chuyển sang frequency domain để tìm thủ phạm

Dùng FFT của oscilloscope, mình thấy ngay một spike rõ ràng ở 200 MHz — và các harmonic nhỏ hơn ở 400 MHz, 600 MHz. Con số 200 MHz nói thẳng với mình: có một clock 200 MHz nào đó đang coupling noise vào mạch analog.

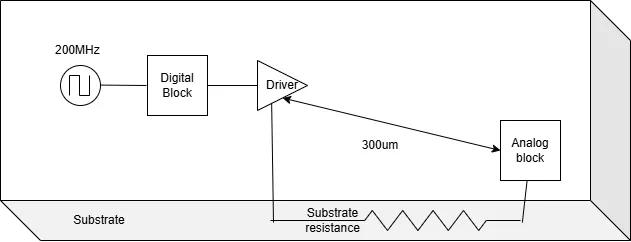

Trace lại floorplan: digital block chạy clock 200 MHz nằm cách analog block khoảng 300 µm trên cùng tấm silicon. Nhìn từ ngoài thì xa, nhưng cả hai đều dùng chung p-substrate bên dưới.

Cơ chế coupling — noise đến từ đâu trong digital block?

Nguồn noise không phải là clock signal trên wire — mà là driver buffer bên trong digital block, tầng inverter cuối cùng drive clock đến các flip-flop.

Mỗi lần clock chuyển từ 0→1 hay 1→0, các transistor bên trong driver switching mạnh — dòng transient lớn chạy qua drain junction của NMOS và PMOS. Drain junction là pn junction, tức nó có — và nối thẳng với p-substrate bên dưới. Dòng transient này coupling vào substrate qua , lan ra xung quanh theo substrate resistance, và cuối cùng đến bulk của transistor analog.

[Hình: Cross-section — driver inverter với Cdb coupling vào substrate, substrate resistance, bulk của NMOS analog]

Khi substrate voltage dao động, của transistor analog thay đổi theo body effect — và đó là nguồn gốc của ripple 2–3 mV ở output.

Tại sao spike ở 200 MHz mà không phải tần số khác?

200 MHz là fundamental frequency của clock — đương nhiên nó có năng lượng lớn nhất. Các harmonic ở 400 MHz, 600 MHz cũng có mặt nhưng nhỏ hơn.

Câu hỏi quan trọng hơn: harmonic nào còn đủ mạnh để gây vấn đề? Driver có rise time , tức bandwidth:

Có nghĩa là harmonic ở 200 MHz và 400 MHz đều còn significant — biên độ của chúng chưa bị attenuate đáng kể so với ideal square wave. Harmonic ở 600 MHz đang ở vùng ranh giới, và các harmonic trên 700 MHz đã bị attenuate mạnh.

Nếu driver có rise time chậm hơn — ví dụ :

Lúc này chỉ còn harmonic fundamental ở 200 MHz là significant — harmonic ở 400 MHz và 600 MHz đã bị attenuate đáng kể. Fundamental vẫn coupling vào substrate như cũ, nhưng các harmonic cao hơn không còn đủ mạnh để gây thêm vấn đề. Đây là lý do slew rate control của driver — cố tình làm chậm rise time — là một kỹ thuật giảm substrate noise mà không cần thay đổi layout.

Bước 3 — Fix trong thực tế: không đơn giản như viết lại code

Lúc này mình biết chính xác thủ phạm và cơ chế. Nhưng fix thật sự thì không dễ.

Thêm guard ring, tăng separation, hay dùng deep n-well để isolate analog block — tất cả những thứ đó chỉ có thể làm trong lần tapeout tiếp theo. Spin lại chip tốn tiền tapeout, tốn thời gian hàng tháng. Không ai phê duyệt spin chỉ vì 2–3 mV noise trừ khi nó block toàn bộ spec của sản phẩm.

Vậy với chip đã tapeout, mình có thể làm gì?

Clock gating có chọn lọc. Nếu digital block có thể gate clock của một số sub-block không cần thiết trong lúc analog đang sampling — đây là fix không tốn chi phí silicon. Nhiều mixed-signal chip có kiến trúc “quiet window” — một khoảng thời gian ngắn mà digital activity bị giảm tối đa để ADC lấy sample sạch.

Slew rate control của driver. Nếu driver có programmable drive strength, giảm drive strength để tăng rise time — bandwidth của tín hiệu giảm xuống, harmonic cao bị attenuate hơn. Trade-off là timing margin của digital signal bị ảnh hưởng, nhưng thường chấp nhận được nếu chỉ cần tăng rise time vừa phải.

Decoupling ngoài chip. Thêm decoupling cap sát chip để giảm noise trên supply rail. Không fix được substrate coupling trực tiếp, nhưng giảm được một phần qua supply bounce.

Tất cả những thứ trên đều là workaround. Fix thật — guard ring, deep n-well isolation, tách power domain — chỉ có trong lần tapeout tiếp theo.

Bước 4 — Câu chuyện giả định: nếu làm đúng từ trước tapeout

Giả sử mình quay lại trước lúc tapeout. Quy trình mà nhiều team AMS dùng — và mình nghĩ là đúng — là đưa noise profile của các block “ồn ào” vào simulation của block nhạy cảm ngay từ giai đoạn thiết kế. Với ví dụ này, block nhạy cảm chính là amplifier đang bị ảnh hưởng — nhưng quy trình tương tự áp dụng cho bất kỳ block analog nào: ADC, bandgap reference, hay LDO.

Bước A — Characterize noise profile của digital block

Từ simulation của digital block, mình extract waveform của substrate current — dòng mà driver inject vào substrate mỗi lần switching. Đây là transient simulation đơn giản: đo dòng chạy qua bulk terminal của các transistor trong driver.

FFT của cho ra noise spectrum: spike ở 200 MHz, 400 MHz, 600 MHz với biên độ cụ thể ở từng tần số. Kết hợp với substrate resistance model — thường lấy từ PDK hoặc extract từ layout tool — mình tính được điện áp noise tại vị trí dự kiến của amplifier:

Với khoảng vài ohm đến vài chục ohm tùy process và khoảng cách giữa hai block.

Bước B — Inject noise vào simulation của amplifier

Thay vì simulate amplifier trong môi trường lý tưởng, mình thêm noise source vào bulk terminal của các transistor nhạy cảm nhất — thường là input differential pair, vì của chúng ảnh hưởng trực tiếp đến offset và gain. Noise source này có waveform lấy từ bước A.

Trong SPICE, cách đơn giản nhất là thêm một voltage source nhỏ vào bulk:

Vnoise_sub bulk_M1 0 dc 0 sin(0 2m 200Meg)

* 2mV tại 200MHz — estimate từ Vsub_noise(f) ở bước ASau đó chạy transient simulation và đo ripple ở output của amplifier — xem nó có vượt quá noise budget không.

Bước C — Quyết định có cần guard ring hay deep n-well không

Nếu simulation cho thấy noise 2–3 mV từ substrate đã tạo ra ripple vượt quá noise budget của amplifier — thì đây là con số cụ thể để justify thêm guard ring hay deep n-well vào layout, dù nó tốn thêm area.

Nếu simulation cho thấy amplifier vẫn đạt spec dù có noise đó — thì mình tapeout với confidence, không phải với hy vọng.

Sự khác biệt giữa hai trường hợp không phải là may mắn hay kinh nghiệm — mà là có hay không có bước simulate với noise profile thực tế trước tapeout. Respin silicon vì substrate noise là một trong những lý do phổ biến và đau nhất trong AMS design, vì nó thường chỉ xuất hiện khi tích hợp đầy đủ — không thấy khi test từng block riêng lẻ.

Bài học: Frequency domain không chỉ là công cụ debug sau tapeout. Nó là công cụ để predict vấn đề từ lúc thiết kế — estimate noise coupling, check separation có đủ không, quyết định có cần deep n-well hay không. Debug bằng FFT sau tapeout là tốt. Dùng frequency domain analysis để không cần debug mới là mục tiêu thực sự.

Tổng kết

Time domain và frequency domain không phải hai thứ riêng biệt — chúng là hai cách nhìn khác nhau vào cùng một tín hiệu. Fourier Transform là cây cầu nối giữa hai domain, và là công thức engineer dùng hàng ngày để đi qua cây cầu đó.

Ba điều cần nhớ:

Thứ nhất: Rise time và bandwidth là hai mặt của một đồng xu — . Đây không phải tần số cao nhất trong tín hiệu mà là tần số cao nhất mà tại đó harmonic còn đủ mạnh để ảnh hưởng đến hình dạng tín hiệu — tức còn “significant” theo nghĩa của Bogatin.

Thứ hai: Rise time ngắn hơn → bandwidth rộng hơn → nhiều harmonic cao hơn trở nên significant. Đây là lý do tăng tốc driver làm tăng EMI và substrate noise — không phải vì năng lượng tổng tăng, mà vì nhiều harmonic cao hơn trở nên đủ mạnh để coupling và radiate.

Thứ ba: Chọn domain phù hợp với câu hỏi đang cần trả lời. Timing và waveform quality → time domain. Noise, EMI, bandwidth, và impedance → frequency domain. Quan trọng hơn, đừng chỉ dùng frequency domain để debug sau tapeout — dùng nó để predict vấn đề từ lúc thiết kế, inject noise profile thực tế vào simulation, và tapeout với confidence thay vì hy vọng.

Tham khảo

- Bogatin, Signal and Power Integrity — Simplified, 3rd ed., Chương 2 — nguồn chính cho bài này. Phần “Bandwidth and Rise Time” và “What Does Significant Mean?” là hai section quan trọng nhất — Bogatin giải thích rất trực quan tại sao và harmonic nào còn significant trong trapezoidal waveform.

- Bogatin, Signal and Power Integrity — Simplified, Chương 1 — đọc trước để có context về signal integrity fundamentals.

- Eric Bogatin’s Signal Integrity Academy — beTheSignal.com — video và webinar miễn phí, tone giải thích tương tự sách.